# PROPOSAL for the SNS RING BEAM SYNCHRONOUS TIMING SYSTEM

# BNL/SNS TECHNICAL NOTE

NO. 048

R. Shafer

September 21, 1998

ALTERNATING GRADIENT SYNCHROTRON DEPARTMENT BROOKHAVEN NATIONAL LABORATORY UPTON, NEW YORK 11973

#### Proposal for the SNS RING Beam Synchronous Timing System

#### R. Shafer 8/20/98; Rev (8/31/98)

#### **Introduction**

The primary purpose of the site-wide SNS synchronization system is to synchronize the various beam-related systems (injector, linac, and the accumulator ring) to the neutron choppers and to the 60-Hz line frequency. The accumulator ring beam extraction pulse must be synchronized to the Fermi neutron choppers, which are very high inertia mechanical rotors, to within about 1 or 2  $\mu$ sec. This extraction must occur within about 5  $\mu$ s after the end of accumulation of a preset number of turns (revolutions) of beam in the ring. In addition, because the linac klystron modulators must be synchronized to the ac line within about ± 1ms, the neutron choppers must be synchronized to the ac line frequency, which varies by as much as ± 0.01 Hz on a minute by minute basis. The beam chopper in the linac MEBT must be synchronized to the accumulator ring to about ± 0.002  $\mu$ s. The proposed conceptual design for this global synchronization system is described elsewhere[1].

The timing synchronization signals, thus obtained, must be broadcast (distributed) to many 100's of systems, located all along the linac, the beam transport lines connecting the linac to the ring and the ring to the neutron target, and around the ring itself.

The need for a ring-specific timing system arises from several factors:

- 1. The ring revolution frequency (about 1.18 MHz) is not harmonically related to the linac frequencies (402.5 and 805 MHz) or to any other frequency used in the SNS beam delivery system.

- 2. The ring revolution frequency is likely to change by up to  $\pm 0.25\%$  during commissioning, and perhaps by  $\pm 0.1\%$  during normal day-to-day operation.

- 3. Several ring-specific systems, and most specifically the beam diagnostic systems distributed around the ring, need to be synchronized to the accumulating beam and to each other with an accuracy in the range of  $\pm 2$  to 4 ns for the entire duration of the accumulation period (about 1000 µs).

- 4. These real-time timing signals must be available around the entire ring, and along both the linac-to-ring and the ring-to-target beamlines.

# Overview of the Ring and Beam Chopper Periods.

The ring has a circumference of about 220.67 m, which for a 1-GeV proton, represents a revolution period of about 841.2 ns. In order to minimize the effects of space charge forces, this revolution period is deliberately selected not to be an integer number of linac RF periods. Thus, as beam is accumulated in the ring, microbunches from the linac, spaced at about 2.485 ns, are interleaved with bunches already injected into the ring.

If the beam energy on the ring reference orbit is changed by +1 MeV, the revolution period changes by about -0.13 ns. If the beam energy changes by +1 MeV, and the ring B (magnetic deflection) field is kept constant, the revolution period changes by about +0.11 ns (note signs). Both variations in the ring period should be expected during normal operation. Over a 1200-turn injection cycle, the injection period will thus be periodically adjusted by up to  $\pm$  150 ns during normal operation. This is about a factor of 50 larger than the tolerable timing error of  $\pm$  2 to 4 ns. During commissioning, the revolution period is likely to change by as much as  $\pm$  2 ns (equivalent to  $\Delta p/p = \pm 1\%$ ), a much more significant amount.

The beam chopper in the linac Medium Energy Beam Transport (MEBT), which produces a gap in the beam that must be synchronous (on average) with the ring period, will be driven by a signal derived from the beam-loaded ring RF cavity[2]. This signal must track any changes in the ring revolution period, and thus will be asynchronous with respect to the linac RF (402.5 and 805 MHz). Because the individual chopper signals must be synchronized to the beam bunching structure to prevent partially chopped bunches from being accelerated, the beam chopper signal from the ring must be "cogged" to the correct linac RF phase using a D-type flip flop being clocked at the beam-bunching frequency[3]. So although the beam chopper is not running on average at an integer subharmonic of the linac RF frequency, this circuit should synchronize the individual beam chopper pulses to the linac RF.

The need for a beam synchronous timing system for the ring.

Triggers for many systems distributed around the ring, including mainly beam diagnostics systems, need to remain synchronous with the beam for the entire 1200-turn injection cycle during small changes in the revolution period. There are two possible ways of accomplishing this:

- 1. Download new delay settings for generating the trigger signals from the control system every time the ring period changes by more than  $\pm 5$  ps. This would be very cumbersome, in part because it is equivalent to a change in beam energy of only 50 keV.

- 2. Use a clock frequency in the timing circuit for generating the trigger signals that is an integer harmonic of the ring revolution frequency (beam synchronous clock). In this system, the delayed timing signals will remain synchronous with the beam without changing the downloaded delay settings.

- 3. In addition to having a beam synchronous clock frequency, the input timing signals to the delay circuits that start the delay clocks (referred to here as "events") need to remain synchronous with the clock phase everywhere it is distributed, for all expected clock frequencies. The best way to accomplish this is to transmit both the clock and the "event" triggers together on the same cable or optical fiber.

This proposed beam-synchronous (beam-sync) timing system is specific to the ring, and its distribution is intended to be limited to ring-specific systems, and to the associated beamlines (linac to ring, and ring to target). This system is not intended to be a substitute for a global timing system, and therefore will primarily be encoded with timing events that are ring specific.

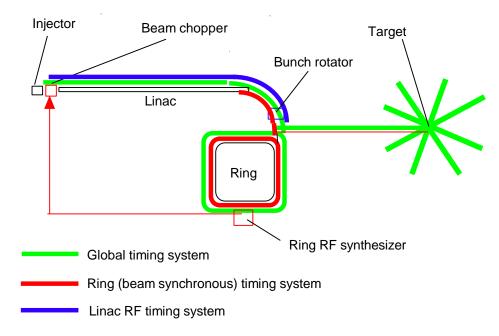

Figure 1 shows the proposed geographical layout of timing signal distribution systems. The red timing system represents the ring system, the blue system represents the linac system, and the

green system represents the global (site-wide) system. These three timing systems are specifically for distributing timing signals that must be distributed on a cycle by cycle (i.e., 60 Hz) basis, and often with a required timing accuracy that is better than a microsecond, and occasionally even a few nanoseconds. Not shown in the Figure are additional (high protocol), real-time datalink (RTDL) systems that distribute time-stamp data (hour, minute, second, etc.), downloaded parameters, and upload data.

Figure 1. Geographical layout of the global (green), linac (blue), and ring (red) timing signal distribution systems.

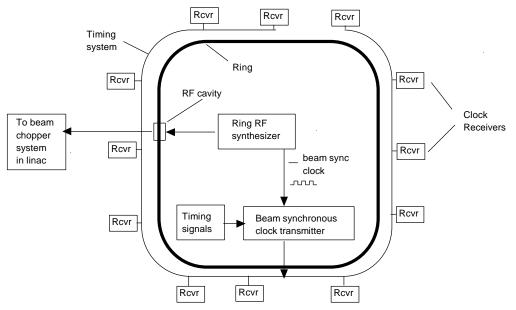

Figure 2 shows the layout for a ring beam-sync timing signal distribution system, including the ring RF synthesizer, the beam-sync signal timing system transmitter, and the receivers distributed around the ring (but not in the tunnel) near the beam diagnostic electronics. The exact details of how the beam-sync clock signal is derived from the RF synthesizer or the RF cavity fanback is not yet determined.

# Outline of proposed beam synchronous timing system

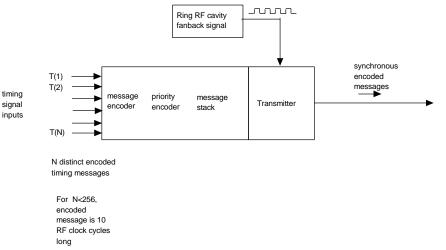

The proposed timing system uses real-time signals ("events") that are synchronously encoded on a continuous pulse train (the "clock") at a suitable harmonic of the ring revolution frequency. The higher the harmonic, the lower the granularity (the clock period), but the higher frequencies are less immune from noise, which in turn produce timing errors. For this discussion, I will assume that the clock frequency is 19.02 MHz, the 16<sup>th</sup> harmonic of the ring revolution frequency. It may be necessary for practical reasons to run the clock at the 8<sup>th</sup> harmonic (9.51 MHz), or the 12<sup>th</sup> harmonic (14.27 MHz). The design I propose for this timing system is the Fermilab Tevatron T-clock system[4]. The selection of the 19.02 MHz clock frequency is for purposes of discussion only, and may change once the detailed operating requirements are reviewed.

On this clock signal, the "events" are encoded as changes in the polarity of individual clock cycles, using a Manchester code or similar encoding technique. Experience has shown that 10 clock cycles (hence 526 ns) is sufficient to encode an 8-bit byte (1 of nearly 256 different "events"), plus 2 synchronization and parity bits. Even though the granularity of this is 53 ns (One-sixteenth of the ring revolution period), the phase of this signal relative to its source is stable to perhaps  $\pm 2$  ns.

Figure 2. Ring layout of a beam-sync timing signal distribution system..

Figure 3 shows a block diagram of the beam sync transmitter. The clock frequency is a constant frequency signal derived from the ring RF synthesizer. Normally, all clock cycles are "0" (zeros), except when events are encoded. The Manchester code (also called phase modulation encoding) represents a "0" as a positive transition at data time, and a "1" as a negative transition at data time. In this way, events are encoded on the clock signal, and suitably designed receivers can regenerate both the original clock frequency and the encoded timing events.

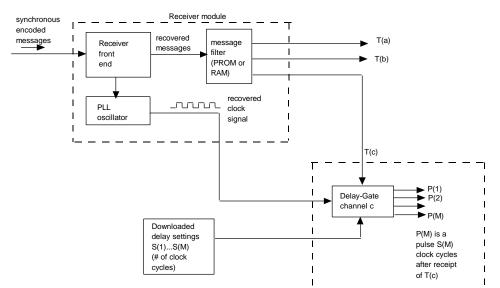

Figure 4 shows a typical receiver circuit. A phase-locked loop (PLL) local oscillator is used to regenerate the clock signal. For this specific case, the local oscillator will operate at 38.04 MHz, twice the frequency of the transmitter (It could just as easily operate at the fourth harmonic of a 9.51 MHz clock signal). This will reduce the granularity of the delay settings (but not the decoded event signal timing), to about 27 ns. The phase of this regenerated clock signal should be stable to perhaps  $\pm 2$  ns. Because the PLL circuit averages over many cycles, the noise contribution to the timing jitter associated with the receiver signal to noise (S/N) ratio will be minimized. The PLL must of course be designed so as to receive and recover clock signals that vary by perhaps as much as  $\pm 1\%$  from the 19.02 MHz ring RF center frequency. Because the encoded events are synchronous with the clock, there is no difficulty with "skewing" of the timing signals with respect to the clock signal, which could be the case if the two signals were distributed on separate cables.

In order to achieve a granularity of 2 ns from the 27 ns granularity of the 36.04 MHz clock signal, a programmable delay generator must be used. Commercial units and chipsets are available to perform presetable delays with 1-ns or better granularity and stability.

Figure 3. Block diagram of a beam-sync transmitter.

Figure 4. Block diagram of a beam-sync receiver.

# Proposed types of event signals

In addition to the real-time trigger signals discussed above, this type of signal broadcasting system is an inexpensive solution for wide dissemination of information signals, such as identifying types of beam pulse cycles (no beam, beam into ring(s), beam into linac beam stop), the status of Fast Protect and Run Permit systems, precursor signals for beam on target, etc. A very early version of this was a site-wide system at LBL (circa 1960), that broadcast a gate signal whenever the 6 GeV Bevaton was accelerating beam, so the nuclear chemists at the Lab could gate off their neutron sensitive NaI(Tl) counters.

As mentioned above, the repertoire of encoded events is necessarily limited (in Fermilab's system) to about 256, in order to minimize the number of bits in each event. Informational events must not be allowed to interrupt or delay time-critical events. There is about 14 ms of no-beam between each beam pulse, when informational events can be broadcast.

#### Time stamping and IOC synchronization

It is likely that IOCs or other hardware will need to time stamp data to a microsecond (or better, in some cases). The time stamp will be a beam pulse number and the number of ring RF cycles after the start of the beam pulse. This is very useful in determining at what point in the pulse errors, beam loss, radiation, etc. are detected.

Also, an event on the clock can be used to synchronize the pulse and clock counters on each IOC. This will assure that when data collected on each IOC can be correlated when read by workstations for analysis.

This system, by its very nature, is not suitable for point to point distribution of a large amount of data to many IOCs. This must be handled by another system. RHIC (BNL) has a RTDL (real time data link) system that can download about 200 parameters in 1.4 msec.

#### Remote IOC and VME resets

With many IOCs distributed around the ring (or the facility), it can be difficult to reload or restart the IOC. The distance between the operator consoles and the VME systems can make a reset operation very time consuming. Different labs have developed procedures to allow the operator to remotely reset a VME system. A reset is needed if there is a hardware or software failure that locks up the system. Also, on a reset, an IOC can download a new version of software. In this mode of operation, new software is installed on a disk, and then the reset is hit to access the software. It provides a quick way to update software for testing or studies. Such a system would require a modification to the Fermilab design to extent the repertoire of events from 256 to several thousand.

# Proposed implementation of the beam synchronous timing system

The Relativistic Heavy Ion Collider (RHIC) project at BNL is implementing a beam synchronous timing system (actually two, one for each counter-rotating beam) that runs at a clock frequency of 14 MHz, and regenerates a clock frequency of 28 MHz (the RHIC RF frequency). This system is synchronous with (clock derived from) the RHIC RF, and has a frequency compliance (range) of  $\pm 0.5$  %[5]. This system design is based on the T-clock system at Fermilab described in reference 4. The RHIC system is described on the web at URL www.RHIChome.BNL.gov/Controls. Specifically, the RHIC beam-sync signal is distributed to 18 alcoves around the 4000-m circumference of RHIC using optical fibers and coax cables. It is implemented in VME. Included in the BNL version is a balanced-line design that is more suitable for long signal transmission lines than the original single-ended design at Fermilab. Module V123 (see description on the web) is the Beam Sync Master (transmitter), and V124 is

the Beam Sync Slave (receiver). Compatible VME modules for beam permit and waveform generation, and digitizing analog signals are also described on the web.

The programmable delay circuit used in the RHIC system to achieve granularity in the 2 ns range is an Analog Devices chip AD9501 (digitally programmable delay generator). This chip can divide the 26 ns regenerated clock periods into as many as 256 programmable steps.

It may be possible to carry over the RHIC designs to the SNS project with only minor modifications to accommodate different clock frequencies. It may be preferable to change the encoding and decoding to accommodate a larger (or smaller) number of events, which will require more extensive redesign. A more complete review of the SNS timing signal distribution requirements is required before this decision can be made.

# **Recommendations**

It is specifically recommended that for reasons related to commonality of design, maintenance, and interfacing to other systems, a common design be adopted for distribution of all the timing signals at SNS, including the global, the ring, and the linac systems proposed in Figure 1.. The RHIC beam sync system appears at this time to be the basis for such a system. The RHIC system is a second-generation synchronous timing signal distribution system, based on the highly successful Fermilab system.

# <u>References</u>

1 D. Gurd, Report of the SNS Timing and Control Group (1998).

2 This signal is referenced to the ring RF cavity fan-back signal. The source of this signal is very important, because small timing errors can be cumulative and therefore fill in the beam gap during a 1200-turn accumulation.

3 The Motorola MC100LVEL29 dual D-type flip flop toggles at 1100 MHz.

4 R. J. Ducar, J. R. Lackey, and S. R. Tawser, "FNAL Booster Intensity, Extraction, and Synchronization Control for Collider Operation," 1987 Particle Accelerator Conference, pages 1937-1939 (1987).

5 Private communication; Brian Oerter (BNL), 8/18/98.